videantis Announces Processing Platform for Fail-Operational Systems

October 25, 2021

News

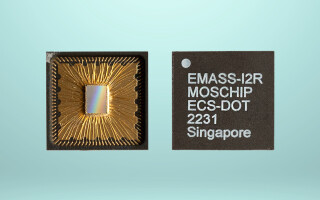

videantis, a supplier of deep learning, computer vision, image processing and video coding solutions, announced availability of its technological platform for fail-operational processing at reduced cost for both smart sensors and highly integrated central ECUs.

videantis v-MP6000UDX processing platform is suited for fail-operational applications such as highly automated driving. With its scalability, it can cover the full range from smart image, Radar, LiDAR sensors (1 to 16 cores) to high-performance AI inference computers (>100 cores).

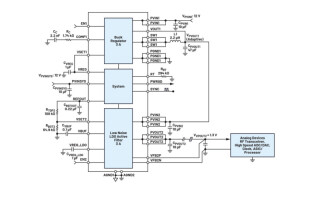

The unified architecture allows the implementation of various functions: video coding, image or graphics processing, computer vision, deep learning using network topologies, or even control functions. Utilizing redundancy, self-test, and other control mechanisms enables customers to build safe systems according to ISO26262 up to ASIL D, using less silicon space or hardware overhead than conventional lockstep architectures.

The concept for this solution was developed within the European PRYSTINE (Programmable Systems for Intelligence in Automobiles) project.

For three years, and equipped with a budget of € 50 Million, about 60 project partners were collaborating to build a Fail-operational Urban Surround perceptION (FUSION) based on Radar and LiDAR sensor fusion and control functions, eventually enabling safe automated driving in urban and rural environments.

The output of this project is designed to help address advanced functional safety requirements on embedded videantis-based multiprocessor systems up to ISO26262 ASIL D. According to the company, compared to traditional lockstep architectures, more than 50% of the cost can be saved due to the reduction of the silicon area.

The cost reduction is achieved by run-time failure detection schemes comprising of core self-test modules and a result monitoring software layer (RMSL) applied to the videantis multiprocessor system. With this, faults can be detected during runtime and processing can be continued while excluding any faulty resource, without the need for duplicate hardware. E.g., with a silicon area overhead of only 3%, a multiprocessing system comprising 32 videantis cores can be turned into a fail-operational processing platform.

For more information, please visit https://www.videantis.com or https://prystine.eu.