SmartDV Delivers New Design IP for Video, Imaging, Entertainment System Protocols

June 04, 2020

SmartDV's standard and custom protocol Design IP is optimized for high performance, low power and minimum area/gate count.

SmartDV delivered a series of video, imaging, and entertainment system Design IP compliant with a variety of standard protocol specifications.

The new Design IP is available for:

- V-by-One, a high-speed serial video interface for HDTV

- VESA DSC (Display Stream Compression), a video compression and decompression standard

- HDCP 2.3 (High-Bandwidth Digital Content Protection) used to encrypt and authenticate digital signals for copyright-protected media, including movies, TV shows and audio

- HDMI CEC (Consumer Electronics Control), a feature of HDMI that allows devices connected to HDMI to be controlled by just one remote

- HDMI eARC (enhanced Audio Return Channel), an HDMI feature that enables high-quality digital audio to be sent back from the TV via HDMI

- CXP (CoaXpress), a high-speed imaging standard for serial transmission of video and still images

SLVS-EC (Scalable Low Voltage Signaling with Embedded Clock), a high-speed serial interface scheme for image data transmission

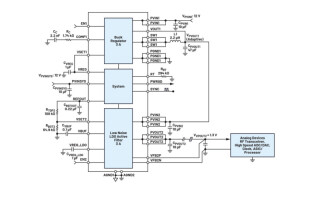

SmartDV's standard and custom protocol Design IP is optimized for high performance, low power and minimum area/gate count. According to the company, ideal customization and delivery of new industry protocols are achieved through SmartDV's proprietary automated compiler-based technology. Custom protocol or modifications to Design IP based on specific customer requests can be developed, validated, and delivered after being fully tested on a field programmable gate array (FPGA) platform.

The SmartDV video, imaging, and entertainment system protocol Design IP is available now. Advanced configuration and status reporting interfaces are supplied, along with a comprehensive test suite that can be implemented in ASIC, system-on-chip (SoC) or FPGA designs.

Pricing is available upon request.

For more information, visit: www.Smart-DV.com