OpenHW Group Announces CORE-V Chassis SoC Project

December 16, 2019

Product

The OpenHW Group aims to tape out a heterogeneous multi-core processor evaluation SoC capable of running the Linux operating system, during the 2nd half of 2020 with the CORE-V Chassis project.

The OpenHW Group aims to tape out a heterogeneous multi-core processor evaluation SoC capable of running the Linux operating system, during the 2nd half of 2020 with the CORE-V Chassis project. The CORE-V Chassis will see a CV64A 64-bit core running alongside a CV32E 32-bit coprocessor core.

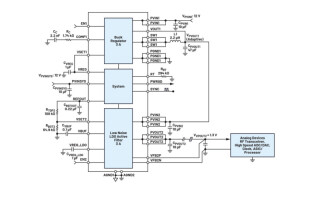

Based on the NXP iMX platform, the resulting CORE-V Chassis evaluation SoC will also feature 3D and 2D GPUs, MIPI-DSI and CSI display and camera I/O, hardware security blocks, PCIe connectivity, a GigE MAC, USB 2.0 interfaces, support for (LP)DDR4, and multiple SDIO interfaces.

The 64-bit CV64A core in the CORE-V Chassis is based on the RV64GC RISC-V core IP, originally developed as part of the PULP Platform at the University of ETH Zurich. Optimized for performance, the CV64A core will be capable of clock frequencies of 1.5GHz and alongside the CV64A, is a highly capable CV32E coprocessor core based on the RV32IMFCXpulp RISC-V core IP, also from the University of ETH Zurich.

Once completed, the CORE-V Chassis is earmarked to form the basis of further multi-core evaluation SoCs. Supported by members of the OpenHW Group, the CORE-V Chassis announcement is an open call for industry participation in this project.

For more information, visit OpenHWGroup.org