Software-Defined Verification and Validation Environment for Complex SoCs

February 24, 2021

Story

Chip design verification is a persistent obstacle that often prevents on-time product delivery. A unified software-enabled verification and validation environment could be the way to break dependencies between hardware design groups and software developers.

With a unified environment, verification could progress with models early on, building the system as different pieces emerge from development. Verification would begin from the outset with final pre-silicon tests focused only on last-minute refinements and full system validation, fast-tracking tape-out, reducing respin risk and simplifying post-silicon verification.

Culprits are increasing complex combinations of hardware and software in a chip, a result of continued “digitalization.” Development of these two fundamental aspects of a system often happen on different schedules. Hardware design, for example, can start as early as two years ahead of software.

The complexity forces hardware verification and validation to include proof that the intended software works correctly on the hardware, a difficult task when software lags so far behind. A software-enabled verification and validation methodology allows earlier hardware verification through early workload analysis, breaking the hardware dependency on system software.

Previously, generic hardware blocks were assembled into a system that could execute software. In that outdated paradigm, hardware design proceeded without consideration of the application software because the hardware was designed to be generic, hosting any number of possible types of software and optimized for none of them.

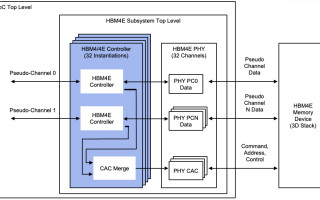

Designers now implement a hardware system in a System-on-chip (SoC) approach. In the past, that hardware system may have been assembled by a system integrator into a self-contained silicon chip that handled the bulk of the computing work. Verification of the full system SoC now must focus on the connection between the underlying hardware and the software it will execute.

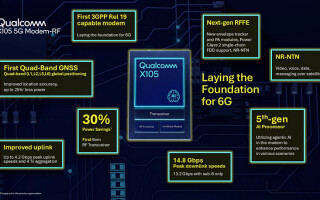

An SoC like this will process specific data workloads for a specific application. Unlike earlier generic processors, the processing architecture must be well suited to the nature of the data it will process. Instruction sets, bus architectures, and the memory/cache structure can be tailored to maximize performance, minimize power and maximize efficiency.

This requires access by hardware engineers to software workloads early in the design cycle. Even the architecture itself needs to be validated for the kind of work to be performed. This dependency on the software has a significant impact on the project schedule, particularly difficult when businesses are trying to “shift left” to bring products to market more quickly.

That’s not all. Other functional and schedule considerations:

-

Business managers want confidence that their product won’t suffer from issues such as poor battery life and still hit the market window

-

Engineering management wants to accelerate the schedule and complete a project within budget, leveraging common methodologies as much as possible

-

Design groups are under pressure to complete increasingly complex designs within 12 to 18 months

-

Verification groups, especially those using hardware emulation, want to parcel out different aspects of the system to different groups for faster parallel subsystem verification

Having this many stakeholders and priorities is driving the urgent need for a better way to complete SoC verification. A software-defined verification and validation environment and methodology will enable engineering groups to deliver complex SoCs, meeting time-to-market windows, providing more thorough checkout, and reducing risk and cost.