Synopsys Introduces RISC-V to its ARC Processor IP Portfolio

November 09, 2023

News

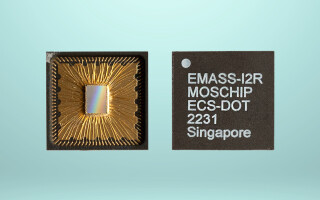

Sunnyvale, California. Synopsys, Inc is expanding its ARC Processor IP portfolio with its RISC-V ARC-V Processor IP. The series will consists of low to high performance options to fit the intended application allowing the flexibility designers need. “RISC-V processors are gaining in popularity as more designers look for greater design flexibility and more options,” said John Koeter, senior vice president of product management and strategy for IP at Synopsys.

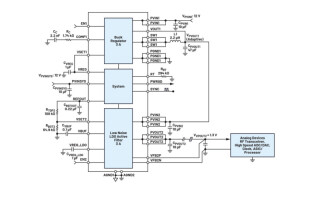

The Synopsys ARC-V Processor IP works with Synopsys MetaWare Development Toolkit, as well as the Synopsys.ai full-stack AI-driven EDA suite to deliver an out-of-the-box development and verification environment for ARC-V-based SoCs.

Errors are detected using the integrated Synopsys ARC-V Functional Safety (FS) Processor IP and adheres to ASIL B and ASIL D safety levels and includes ISO 26262 functional safety and ISO 21434 automotive cybersecurity qualifications.

Calista Redmond, CEO, RISC-V International, said, “Synopsys ARC-V Processor IP, combined with the company’s co-optimized EDA and verification solutions, contribute to greater flexibility and choice in the RISC-V ecosystem for the benefit of chip design across industries.”

Features:

- 32-bit and 64-bit ARC-V Processor IP

- MetaWare software development toolchain

- Synopsys.ai full-stack AI-driven EDA suite

- Fusion QuickStart Implementation Kit

- Verification solutions (hardware-assisted verification

and virtual prototypes, speed verification, validation, and software development)

For more information, visit synopsys.com.