Integrate dynamic voltage and frequency scaling into instruction-accurate virtual platforms

March 02, 2017

In embedded systems, extra-functional requirements, such as power consumption, have been increasing in importance. In a cooperative effort between OFFIS and Imperas Software, the Open Virtual...

In embedded systems, extra-functional requirements, such as power consumption, have been increasing in importance. In a cooperative effort between OFFIS and Imperas Software, the Open Virtual Platforms (OVP) technology has been equipped with support to express and execute dynamic voltage and frequency scaling (DVFS) compatible power models. Software on the virtual platform can access the actual power consumption and perform power management through DVFS. The technology has been successfully demonstrated for an ARM-based multi-core platform, running a synthetic bare-metal DVFS test application and Linux power management.

OFFIS was founded in 1991 as a not-for-profit organization by the State of Lower Saxony, the University of Oldenburg, and professors of the departments of computer science and related faculties. OFFIS is dedicated to technology transfer, and is organized in three R&D divisions, focusing on IT in Transportation, Health and Energy. Imperas Software is a team of simulation and tool technologists combined with embedded software applications professionals.

The technology baseline is the OVP-based models, and the simulator engine, multiprocessor debugger, and software analysis tools from Imperas. A virtual platform is a software simulation of a (multi-)processor-based system, which includes Instruction Accurate (IA) processor models connected with models of memories and peripheral components. The overall memory layout of such a platform is fully target compatible, required to execute the target binary of embedded software for the purposes of rigorous functional verification. Essentially the target software stack does not know that it’s not running on the hardware.

The advantages of virtual platforms over hardware-based development and debug environments include full controllability and observability in the software simulation environment, deterministic software execution, ease of test automation, and earlier simulation environment availability. Not that hardware-based environments should be replaced by virtual platforms, but the two technologies are complementary in the embedded software flow.

The key to this solution is to ensure that the virtual platform executes code as efficiently and quickly as possible. This requires high quality simulation models of processors, peripherals, and behavioural components, plus the simulation engine that executes those models, to execute embedded software up to a billion instructions per second. For many embedded processor platforms, Imperas technology can execute software running faster than real time.

The goal of the cooperation between OFFIS and Imperas is the integration of power models into the overall Imperas and OVP modeling and simulation framework to support functional testing of the power management configuration and the actual power management functionality. To control the power characteristics and the impact on execution speed, the first step to make OVP models power aware is to add supply voltage (Vdd), clock frequency, and a “derate” function to the CPU models. Derate simply reduces the simulated number of instructions in relation to the processor’s set clock frequency.

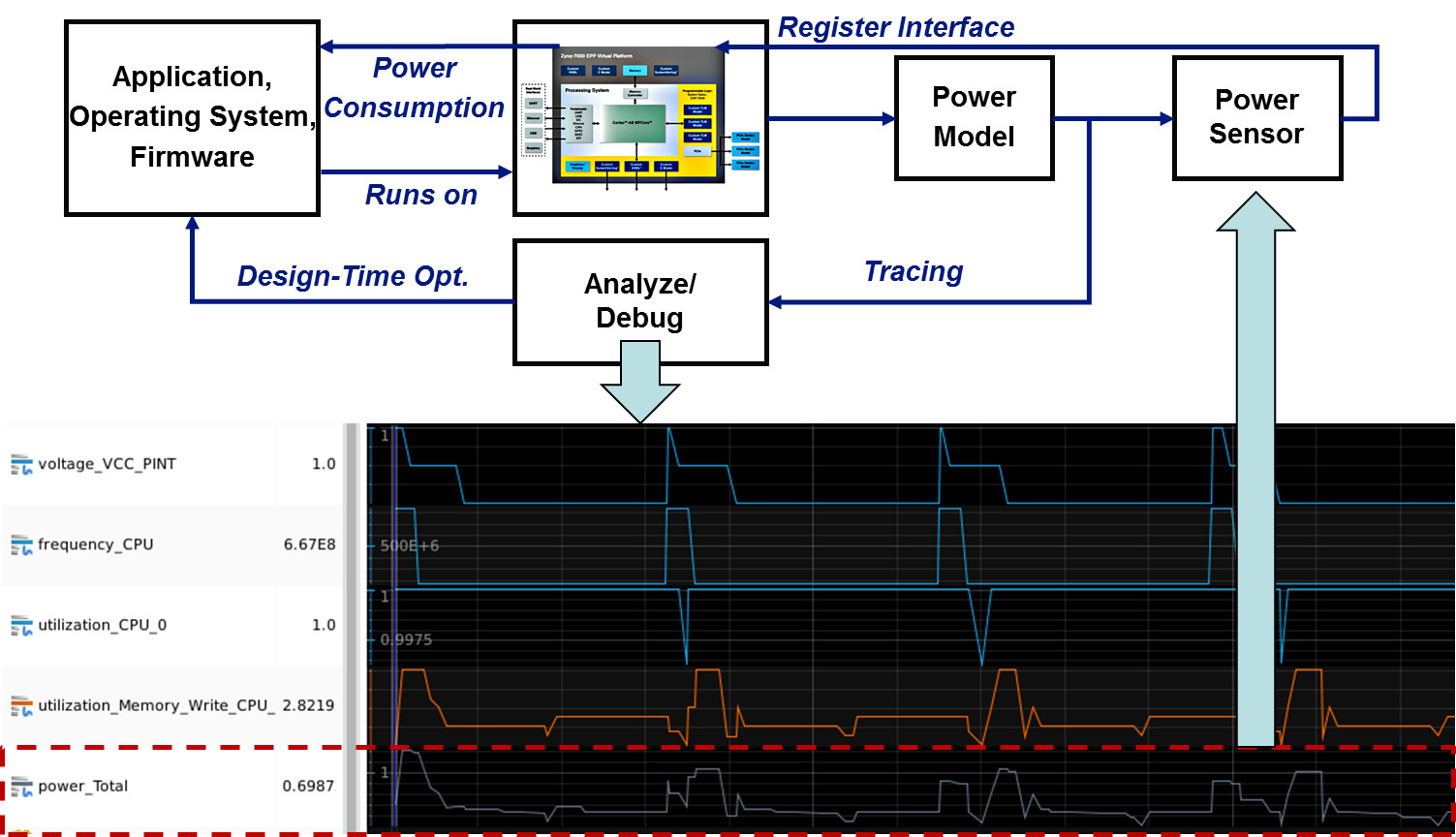

The technology developed by OFFIS is called timed-value-streams (TVS), and with it, arbitrary state- or process-related units can be recorded, combined, aggregated, and traced over time. The TVS technology has been successfully applied within OVP to collect functional activity traces from the processor (e.g. processor load, idle instructions, and wait for interrupt), memory subsystem (e.g. read/write accesses, access of different banks), bus system (e.g. read/write transaction, length of transaction), and peripherals components. Together with the newly integrated and software-configurable supply voltage and clock frequency (dynamic voltage and frequency scaling), a power model was realized for the ARM dual core processor (ARM Cortex-A9MPx2) subsystem of the Xilinx Zynq SoC. The applied combination of activity, and voltage and frequency traces, has been structured hierarchically, e.g. to represent different SoC power domains or chip power rails.

The power information can be written into a VCD (Value Change Dump) sink to display it for analysis. As mentioned, power information can be fed into a power sensor that can be mapped into the hardware platform’s address space and thus allow software access to derive power-management decisions at run-time.

This overall applied mechanism is depicted in the figures. The visibility of dynamic physical properties such as the power in this example, we can observe the effect of power management using DVFS, the power consumption, and the performance of the application in a purely virtual prototype.

The video below shows the booting of Linux with an attached power model and a synthetic bare-metal DVFS test application, with a reading from the virtual power sensor.

[youtube=https://youtu.be/LDt4nd4mAyc]

R. Görgen, K. Grüttner, and S. Schreiner of OFFIS and D. Graham of Imperas were all very instrumental in the writing of this article.