MIPI Releases I3C v1.1 Utility and Control Bus Upgrade for I2C Implementers

January 16, 2020

News

New version further simplifies development for smartphones, IoT devices, automotive/ADAS, server manageability and more.

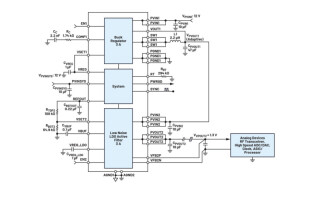

MIPI Alliance announced MIPI I3C v1.1, the first update to its interface. MIPI I3C v1.1, available now to MIPI members, is a scalable, medium-speed utility and control bus that connects peripherals to an application processor. This streamlines integration and improves cost efficiencies in the integration of mechanical, motion, biometric, environmental, and other types of sensors.

MIPI I3C v1.1 builds on existing capabilities with new features for peripheral command, control, and communication to a host processor over a short distance. It also provides extra bus lanes to increase the interface speed to near 100 MHz.

Other features include, grouped addressing, enhanced error detection/recovery, slave reset, comprehensive flow control, outside end transfer and new command, control, and communication (CCC) capabilities.

Additional system-solution resources have also been introduced to support the I3C ecosystem:

- MIPI Discovery and Configuration (MIPI DisCo) for I3C – A framework designed to simplify software integration of sensors and other peripherals that use the MIPI I3C device interface by allowing major operating systems to identify MIPI-conformant external devices and automatically implement drivers for them.

- MIPI I3C Host Controller Interface – This defines a common set of capabilities for the host controller and the software interface. An update to the interface that supports v1.1 is currently in development.

- MIPI Debug for I3C – A baremetal, minimal-pin interface for transporting debug controls and data between a debug and test system (DTS) and target system (TS). It is scheduled for release later this year.

- FAQs, an application note, and conformance test suite (CTS) are being developed to include v1.1.

MIPI will host a webinar on February 12, 2020, at 8 am Pacific to further explore the features and benefits of MIPI I3C v1.1 and provide an update on the I3C ecosystem. To register, visit http://bit.ly/2t56SVD.

For more information, visit www.mipi.org.