Simplifying Design Verification for Increasingly Custom RISC-V Processors

December 10, 2021

Story

RISC-V is known as an open-standard instruction set architecture (ISA) whose base instructions have been frozen to minimize complexity. But more recently it has added a wide range of custom extensions and enhancements that are making it increasingly popular amongst SoC designers building application-specific systems.

The custom functionality adopted in these architectures is often enhanced with a hardware/software co-design strategy that optimizes software to maximize the specialized capabilities of the RISC-V processor IP.

But whether the system is developed in a hardware/software co-design environment or not, the process of building a stable SoC design and verification flow still involves significant setup and time-consuming manual alterations. Research estimates SoC verification consumes 50-80% of total SoC design time and cost – and there is even more work for verification engineers working with RISC-V processors than Arm SoCs because the CPU itself, along with any customizations, must also be verified.

“The increasing popularity of open-source IP is also contributing to growth in teams undertaking verification as an incoming quality inspection as part of the initial phase of an SoC project,” a recent statement from Imperas, a provider of hardware design verification, RISC-V processor models, and virtual prototypes for software simulation, reads. “Plus, the design option to modify or extend base core functionality will depend on a working design verification framework from the start.”

Normalizing Verification Around Customizable RISC-V IP

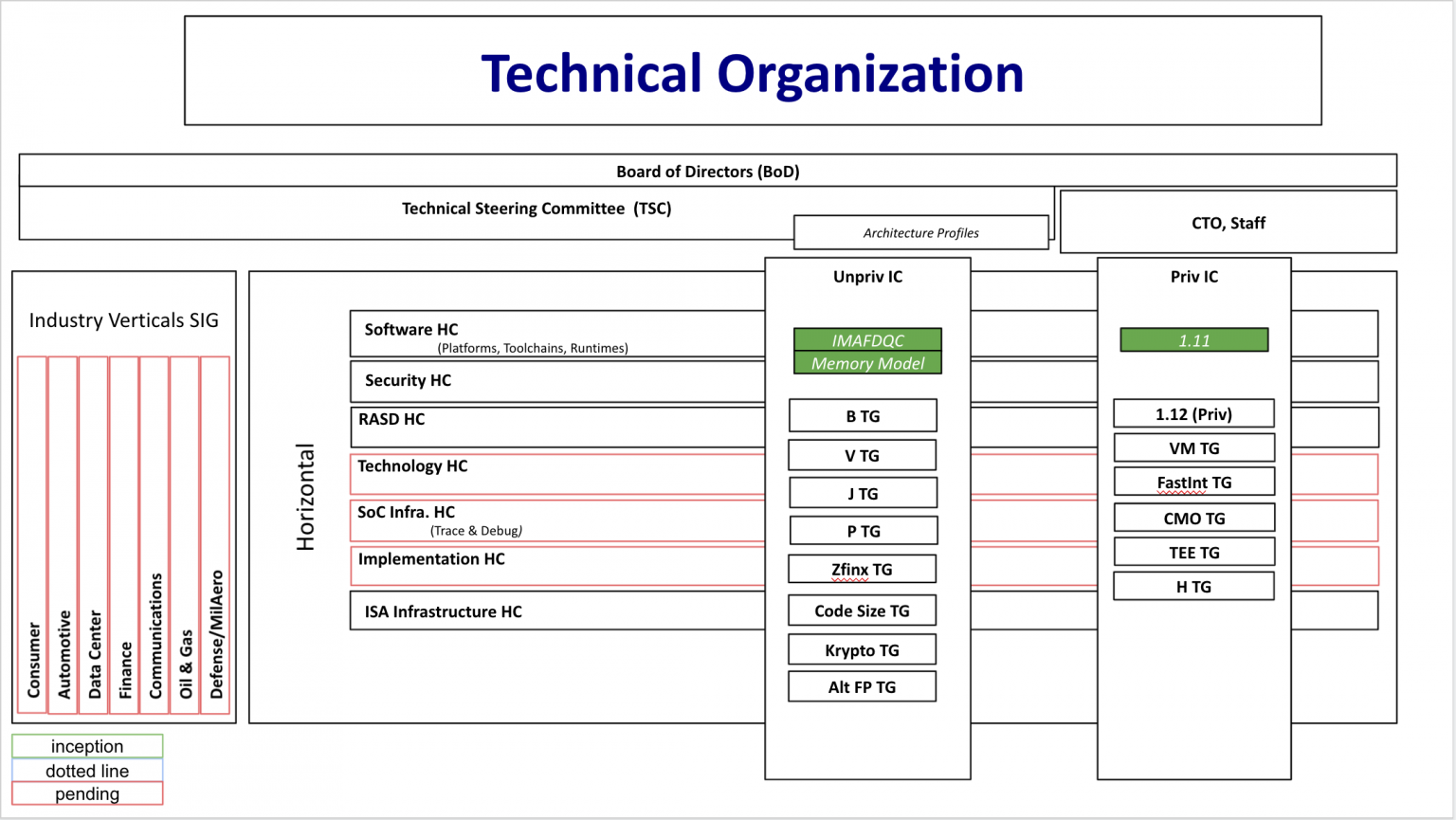

Indeed, as RISC-V matures more and more design teams are opting to “modify or extend base core functionality,” so much so that the RISC-V Foundation has organized special interest groups to normalize extended feature sets for target use cases. These working groups can be seen on the left side of the below diagram, many of which have transitioned from pending to active since the table’s publication in the spring.

In response, the ImperasDV tool is looking to simplify the RISC-V SoC design verification process through “golden reference models” that are compatible with current UVM SystemVerilog techniques. It features an environment with a lock-step-compare design verification methodology that allows a device under test (DUT) programmed in Verilog or SystemVerilog to run and build assembly-level programs. This helps address asynchronous events, which in turn reduces debug analysis time in the event an error is found.

The tool’s principal components are:

- Instruction test generator

- RTL DUT subsystem

- Functional coverage measurement

- Test bench/harness

- Imperas DV subsystem

The tool’s envelope accommodates the entire RISC-V ISA, including privileged mode of operation, and is compatible with the latest Vector, DSP/SIMD, Bitmanip, and Crypto (Scalar) extensions. From an architectural point of view, ImperasDV provides a verification environment that supports the RISC-V Verification Interface (RVVI) standard. This simplifies integration between customer RTL, the reference model, and the testbench.

As mentioned, the integration facilitates lock-step-and-compare verification for complex superscalar pipelines, and the platform can accommodate multiple hardware threads and complete instructions out-of-order. Imperas’ golden reference models ensure that operational data evaluated by the platform executes correctly, even across different versions thanks to configurable version control support for specific revisions.

Open-Source Co-Design Starts Now

The ImperasDV RISC-V verification toolchain has been adopted by many of the semiconductor industry’s leading RISC-V suppliers, some of whom already have working silicon prototypes and are now working on second-generation designs. These include Codasip, EM Microelectronics (Swatch), NSITEXE (Denso), Nvidia Networking (Mellanox), OpenHW Group, MIPS Technology, Seagate Technology, Silicon Labs, and Valtrix Systems, plus others yet to be made public.

Of course, we have yet to address the other side of the hardware/software co-design equation: embedded software development. Here, Imperas is also accelerating design cycles through modeling and simulation solutions, only these are based on open-source Open Virtual Platform (OVP) models.

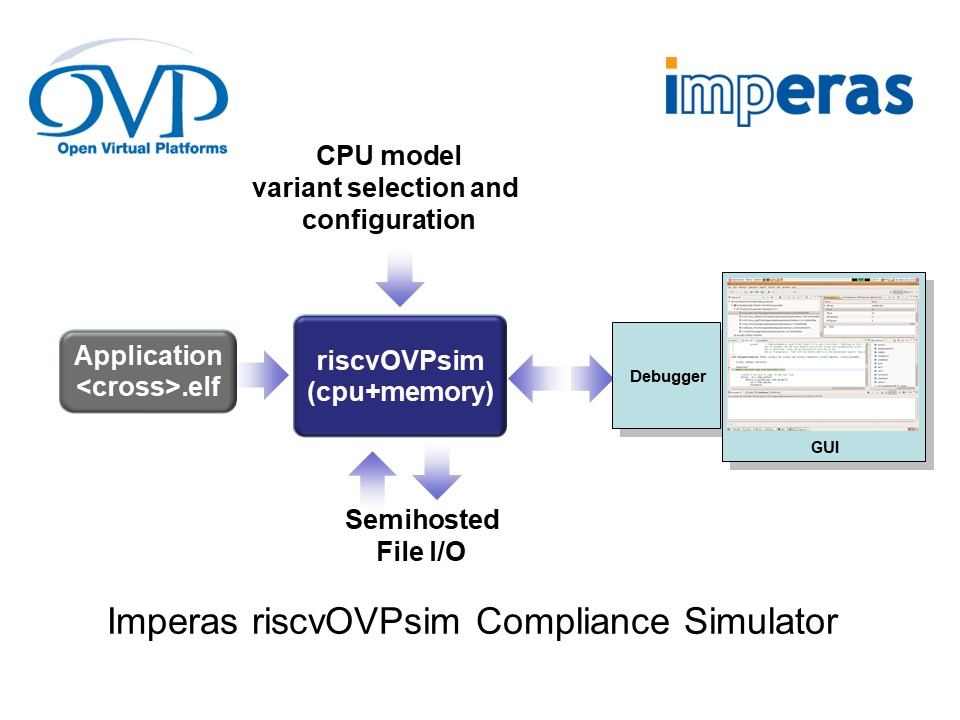

The company’s riscvOVPsim instruction set simulator (ISS) permits development and debug of code targeting RISC-V processor targets at speeds of up to 1,000 MIPS. It leverages Imperas’ OVP Fast Processor Model library to deliver instruction-accurate single-core RISC-V configurations and variants and is even used by the RISC-V Foundation’s compliance framework and test suite.

Best of all, riscvOVPsim can be downloaded for free from GitHub, and an enhanced test suite that includes new RISC-V vector extensions can be found at www.ovpworld.org/riscvOVPsimPlus.

Available upgrades to riscvOVPsim include Virtual Platform Development and Simulation, Multi-Core Software Development, Extendable Platform Kits, and the QuantumLeap MultiProcessor target on MultiProcessor host (MPonMP) acceleration software.

The Imperas portfolio, along with other tools coming out of the quickly evolving RISC-V ecosystem, provide more than enough to get started on your own open processor design today.

More information can be found at www.imperas.com/imperas-riscv-solutions.